# WAN : Bloc

La transmission synchrone est caractérisée par l'échange de **blocs de données** très souvent protégés par une **information redondante**.

Elle diffère donc quelque peu du cas particulier étudié avec le convertisseur asynchrone-synchrone.

## 1 Blocs orientés caractères

(Binary Sync. Communicat. d'IBM)

Ils utilisent des caractères spéciaux pour indiquer le début (STX : start of text) et la fin (ETX : end of text) d'un message :

|     |     |      |     |     |

|-----|-----|------|-----|-----|

| SYN | STX | DATA | ETX | BCC |

|-----|-----|------|-----|-----|

|      |                                                                                                  |

|------|--------------------------------------------------------------------------------------------------|

| SYN  | contient le caractère de synchronisation (SYN=\$16)                                              |

| STX  | marque le début du bloc (start of text)                                                          |

| ETX  | marque la fin du bloc (end of text)                                                              |

| DATA | contient les caractères du message <b>qui doivent être différents de SYN, de STX et de ETX !</b> |

| BCC  | contient l'information redondante (Block Check Control)                                          |

## 2 Blocs orientés octets :

|     |       |      |     |

|-----|-------|------|-----|

| SYN | COUNT | DATA | CRC |

|-----|-------|------|-----|

|       |                                                                                                   |

|-------|---------------------------------------------------------------------------------------------------|

| SYN   | contient le caractère de synchronisation                                                          |

| COUNT | donne la taille du bloc                                                                           |

| DATA  | contient les octets du message; qui peuvent prendre n'importe quelle valeur (même celle de SYN !) |

| CRC   | contient l'information redondante (Cyclic Redundancy Check)                                       |

### 3

## Parité bloc

Principe : disposer en colonne un nombre déterminé de caractères (bloc) et compléter (dans le cas de BSC par exemple)

- chaque ligne par un bit de parité impaire

- chaque colonne par un bit de parité paire

Format d'un bloc orienté caractère avec comme message les caractères ASCII AEV; STX = 02H, ETX = 03H

|     |   |   |   |   |   |   |   |

|-----|---|---|---|---|---|---|---|

| STX | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| A   | 1 | 0 | 0 | 0 | 0 | 0 | 1 |

| E   | 1 | 0 | 0 | 0 | 1 | 0 | 1 |

| V   | 1 | 0 | 1 | 0 | 1 | 1 | 0 |

| ETX | 0 | 0 | 0 | 0 | 0 | 1 | 1 |

| BCC |   |   |   |   |   |   |   |

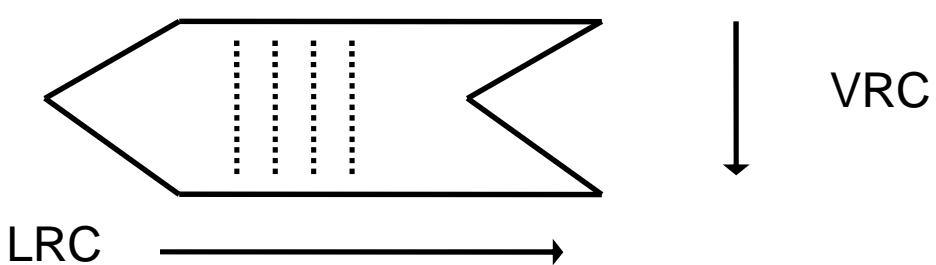

La disposition des caractères sur une bande perforée explique l'origine des appellations :

VRC : Vertical Redundancy Check

LRC : Longitudinal Redundancy Check

## 4      Code cyclique redondant

- a) Message et diviseur sont représentés par un polynôme :

- message :  $M(x) = x^4 + x + 1$       diviseur :  $G(x) = x^2 + 1$

- |   |   |   |   |   |

|---|---|---|---|---|

| 1 | 0 | 0 | 1 | 1 |

| 1 | 0 | 1 |   |   |

- b) Génération du code cyclique à l'émission :

- soit  $r$  le degré de  $G(x)$ , ajouter  $r$  bit à "0" à la fin du message

- |   |   |   |   |   |   |   |

|---|---|---|---|---|---|---|

| 1 | 0 | 0 | 1 | 1 | 0 | 0 |

|---|---|---|---|---|---|---|

- (il s'agit en fait du produit  $x^r * M(x) = x^2 * (x^4 + x + 1)$

=  $x^6 + x^3 + x^2$

- diviser par  $G(x)$  **modulo 2** :

- 1 0 0 1 1 0 0 :    1 0 1

données transmises (message et redondance) :

1 0 0 1 1 1 0

- c) Contrôle à la réception :

- diviser par  $G(x)$  modulo 2 :

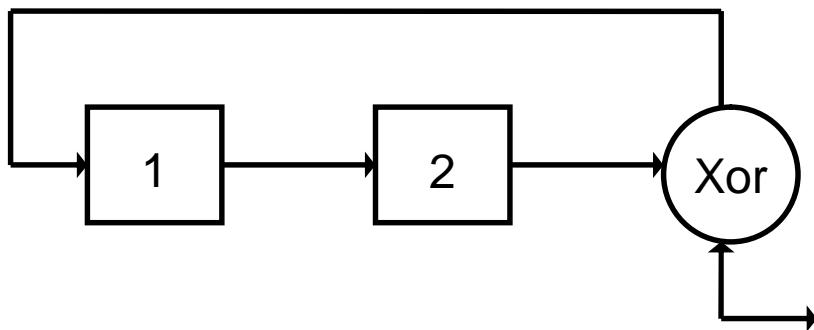

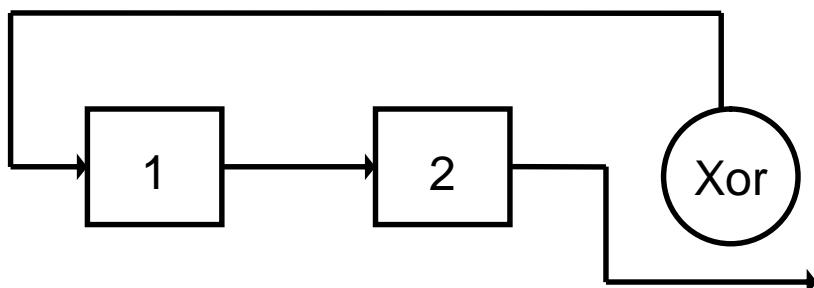

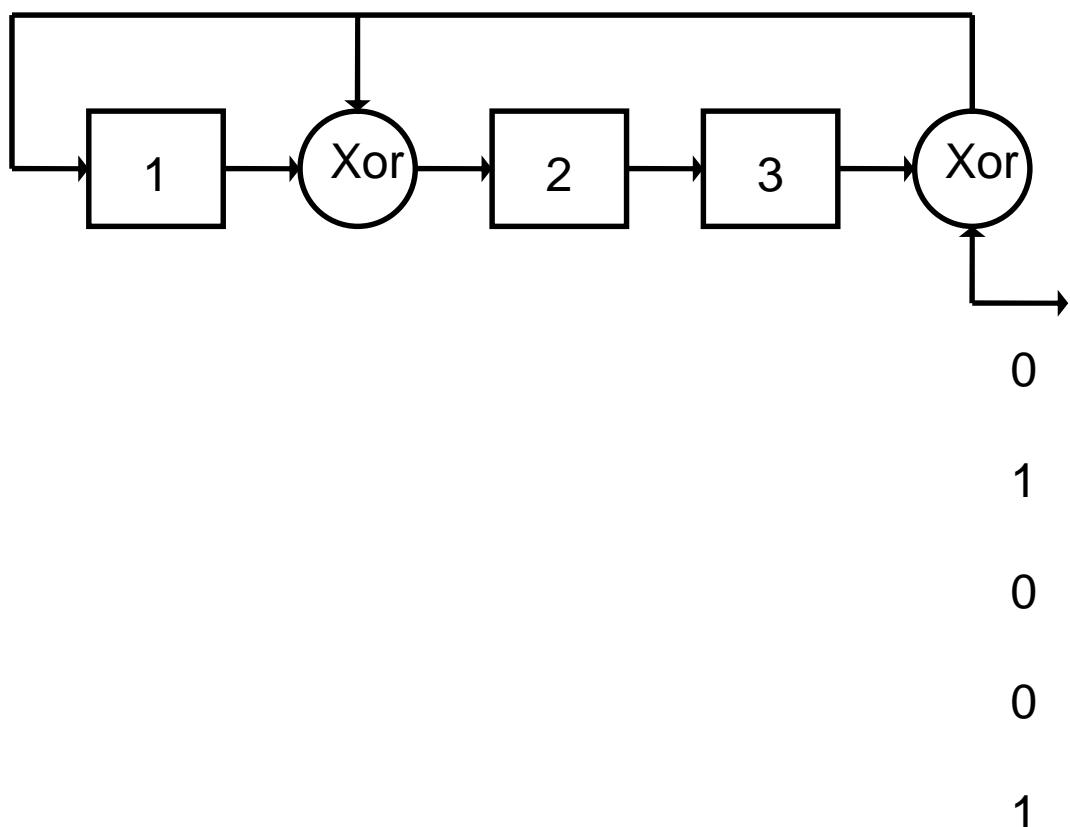

- d) Le circuit logique suivant composé de registres à décalage (Shift) et d'une porte OU exclusif (Xor) effectue cette division

|             |   |   |   |

|-------------|---|---|---|

| mise à zéro | 0 | 0 |   |

| Xor         | 1 |   | 1 |

| Shift       |   | 1 | 0 |

| Xor         | 0 |   | 0 |

| Shift       |   | 0 | 1 |

| Xor         | 1 |   | 0 |

| Shift       |   | 1 | 0 |

| Xor         | 1 |   | 1 |

| Shift       |   | 1 | 1 |

| Xor         | 0 |   | 1 |

| Shift       |   | 0 | 1 |

- e) Le contenu des registres à décalage (redondance) est ensuite transmis :

données transmises (message et redondance) :

1 0 0 1 1 1 0

----->temps

f) Le contrôle à la réception commence **comme en d)** puis :

Xor

Shift

Xor

Shift

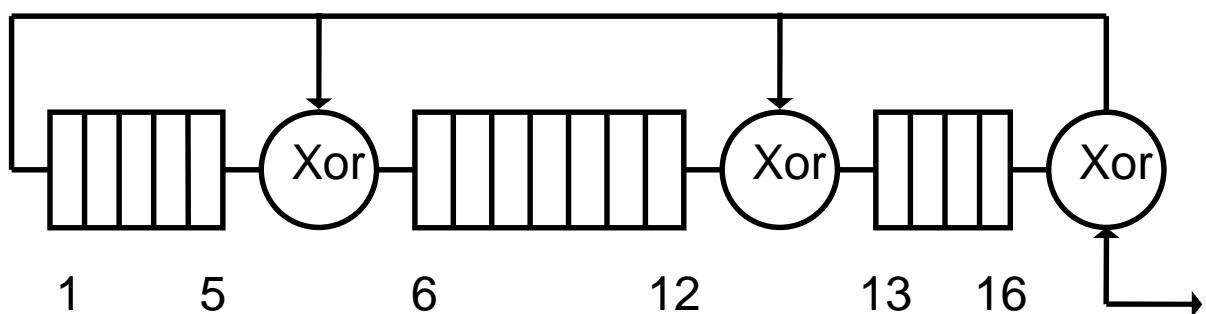

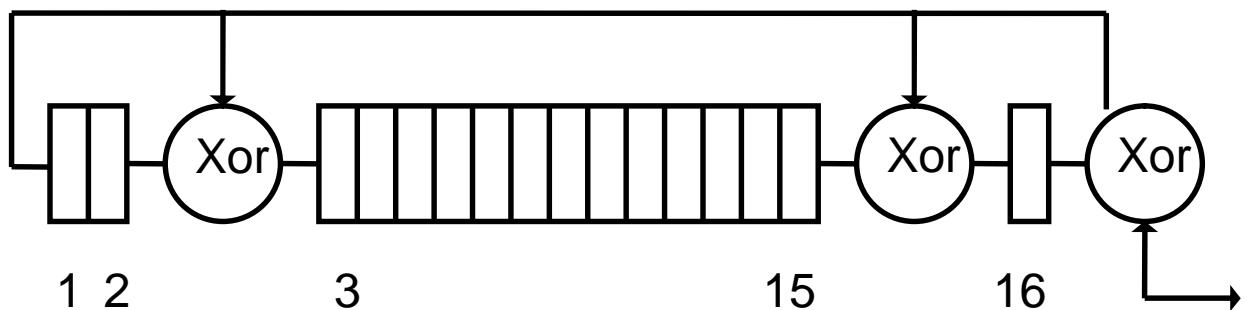

g) Polynômes G(x) utilisés pratiquement de degré 16 :

$$x^{16} + x^{12} + x^5 + 1 \text{ (CRC-CCITT)}$$

$$x^{16} + x^{15} + x^2 + 1 \text{ (CRC-16)}$$

**Ex 3 :**  $G(x) = x^3 + x + 1$      $M(x) = 0 \ 1 \ 0 \ 0 \ 1$

**h) Illustration avec le circuit MC 8503**

## 5      Blocs orientés bits (Bit Oriented Protocol)

Ils permettent le transfert d'un message de X [bit] :

FLAG (drapeau) sert à la fois de caractère de synchronisation et de **marque de début et de fin de bloc**

valeur binaire : 0111110 hexa : 7EH

DATA contient le message de X bit

CRC contient l'information redondante

Pour **distinguer le drapeau d'une suite de bits identiques** dans le bloc, l'émetteur insère un bit "0" après toute suite de 5 bits à "1".

Ce bit supplémentaire est détruit par le récepteur pour régénérer la suite initiale.

Ce mécanisme garantit ainsi la **transparence** des données :

|         | EMETTEUR | TRANSMIS  | RECEPTEUR |

|---------|----------|-----------|-----------|

| DRAPEAU | 0111110  | 0111110   | 0111110   |

| DONNEE  | 0111110  | 011111010 | 0111110   |

Il est possible, en cours d'émission, de signaler que le bloc doit être annulé (Abort) en plaçant au moins 7 bits consécutifs à "1".